Available Online at www.ijcsmc.com

# **International Journal of Computer Science and Mobile Computing**

A Monthly Journal of Computer Science and Information Technology

ISSN 2320-088X IMPACT FACTOR: 5.258

IJCSMC, Vol. 5, Issue. 3, March 2016, pg.659 - 666

# ARITHMETIC UNIT BASED RECONFIGURABLE APPROXIMATION TECHNIQUE FOR VIDEO ENCODING

# J.Jayakodi

ECE (Final year)

jayakodiece@gmail.com

IFET College of Engineering

Mr. K.Sagadevan M.E Senior Assistant Professor Department of ECE sakakec@gmail.com

Abstract: The research community in the last few years from the field of approximate computing has received significant attention, particularly in the context of different signal processing. Image and video compression algorithms such as JPEG, MPEG and so on, which can be exploited to realize highly power-efficient implementations of these algorithms. However, existing approximate architectures typically fix the level of hardware approximations statically and are not adaptive to input data. This project addresses this issue by proposing a reconfigurable approximate for MPEG encoders that optimizes power consumption with the aim of maintaining a particular peak signal-to-noise ratio threshold for any video. I design reconfigurable adder/subtractor blocks, and subsequently integrate these blocks in the motion estimation and discrete cosine transform modules of the MPEG encoder. I propose two heuristics for automatically tuning the approximation degree of the RABs in these two modules during runtime based on the characteristics of each individual video. Dynamically adjusting the degree of hardware approximation based on the input video respects the given quality bound PSNR degradation across different videos while power saving a dual mode full adder is greater than the full adder, when compared to existing implementations.

Index terms- approximate circuits, low power design, approximate computing, quality configurable.

## I. INTRODUCTION

Digital signal processing (DSP) blocks from the Backbone of various multimedia applications used in portable devices. Most of the DSP blocks implement image and video compression algorithms. Approximate computing architectures exploit the fact that a small relaxation in output correctness can result in significantly simpler and lower implementations. However, most approximate hardware architectures proposed so far suffer from the limitation that, for widely varying input parameters, it becomes very hard to provide a quality bound on the

output, and in some cases, the output quality may be severely degraded. The main reason for this output quality fluctuation is that the degree of approximation (DA) in the hardware architecture is fixed statically and cannot be customized for different inputs. This paper adopts a different approach to addressing this problem by dynamically reconfiguring the approximate hardware architecture depending on the inputs. Following contributions are

- 1) I demonstrate that, for a fixed level of hardware approximation in an MPEG encoder, the output quality varies widely across different videos, often going below acceptable limits. This shows that setting the level of hardware approximation statically is insufficient.

- 2) I investigate, for this paper, the use of dynamically reconfigurable approximate hardware architectures that vary the degree of approximation during run-time across multiple computational cycles, depending on the inputs.

- 3) Toward this end, I propose the design of reconfigurable adder/subtractor blocks for four commonly used adder architectures, viz, ripple carry adder, carry look ahead adder, carry bypass adder, and carry select adder, and subsequently integrate them into the MPEG encoder to enable quality configuration execution.

- 4) I propose a design methodology to adapt a degree of approximation dynamically based on the characteristics with the main aim of maintaining the output quality.

- 5) I have implemented the proposed architecture for an MPEG encoder on an Dual mode full adder (DMFA). My experimental results show that the proposed architecture results in power savings compare to a baseline approach that uses reconfigurable approximate architecture with the goal of maintaining a particular peak signal-to-noise ratio (PSNR) threshold for any video.

#### II. RELATED WORKS

There has been a lot of effort in constructing energy-efficient video compression schemes. Different methods of power reduction include algorithmic modification[1],[2],voltage overscaling[3] and imprecise computation of metrics[4]. Approximate computing methods achieve a large amount of power savings by introducing a small amount of error or inaccuracy into the logic block. Different approaches for approximation include error introduction through voltage overscaling.[5],[6]. Intelligent logic manipulation[7] and circuit simplification using don't care based optimization techniques[8].

The methods in [9] and [10] introduce imprecision by replacing adders with their approximate counterparts. There also exist instances of approximations introduced in the MPEG encoder[5],[11]-[13]. Most of them exploit the inherent error resilience of the motion estimation algorithm which results in minor quality degradation. For example [11] use a bit width compression technique to reduce power consumption video frame memory [12] and [13] use bit truncation to introduce approximations in the ME block of the MPEG encoder. Note that, a preliminary version of this paper appeared in [14]. Finally, we provide a comparative study of the power consumption of the different RAB s and also demonstrate how the DA is automatically regulated across different frames during runtime.

### III. BACKGROUND

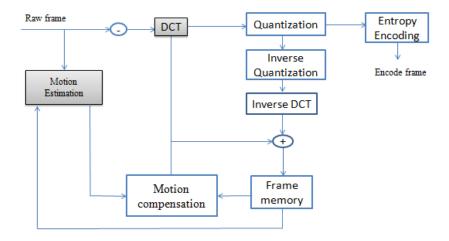

## I. MPEG compression scheme

MPEG is mostly preferred for the video compression scheme in modern video devices and applications. MPEG-2/MPEG-4 standards are used to squeezed to very small sizes. MPEG uses both Interframe and Intraframe encoding for video compression. Intraframe encoding involves encoding the entire frame of data, while Interframe encoding utilizes predictive and interpolative coding techniques as means of achieving compression.

The interframe version exploits the high temporal redundancy between adjacent frames and only encodes the differences in information between the frames, thus resulting in great ratios. In this case, the encoding takes placed based upon the differences between the current frame and previous frame in the video sequence.

Fig.1 MPEG encoder block diagram

There are three kinds of frames used in MPEG encoding:

- 1. I-frames means intraframe encoded.

- 2. P-frames means predictive encoded.

- 3. B-frames means bidirectional encoded.

An I-frame is encoded as it is without any data loss and usually precedes each MPEG data stream. P-frames are constructed using the difference between the current frame and the immediately preceding I or P frame.

B-frames are produced neighbor to the closest two I/P frames on either side of the current frame. The I, B and P frames are compressed when subjected to DCT. It is used to remove the existing frame. A significant portion of the interframe encoding is spent in calculating motion vectors (MVs) from the computed differences.

Every non encoded frame is divided into Macro blocks (MBs), such as  $16 \times 16$  pixels. The Motion vectors (MVs) actually contain the information regarding the relative displacements of the Macro blocks (MBs) in the present frame in comparison with the reference.

#### Quality of a video

The advantage of encoding operation s used to find from the output quality of the decoded video peak signal-to-noise ratio (PSNR), SAD, and so on are used to measuring the quality of video. PSNR metric as a means of video quality estimation. PSNR of a video means the average PSNR over a constant number of frames (50) of the video.

#### IV. PROPOSED ARCHITECTURE

Reconfigurable Adder/Subtractor Blocks

In degree of approximation is dynamically varied which can be done when each of the adder/subtracter blocks with one or more of its approximate copies. Reconfigurable Adder/Subtractor blocks is able to switch between them as per requirement and can include any approximation version of this blocks.

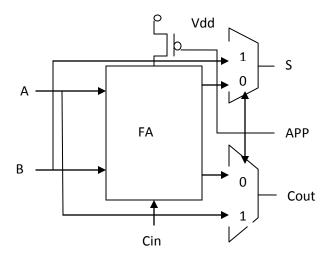

1-bit dual mode full adder is consists A, B, Cin are the inputs and outputs are Sum = A and Cout = A. When each full adder (FA) cell of the adder/subtractor with a dual-mode full adder (DMFA) from the proposed scheme. In which each full adder cell can perform operating either in fully accurate or in some approximation mode depending upon the state of the control signal APP. When operating in the approximate mode the full adder act as power gated.

Dual-mode full adder can operated in either the two approximation modes. Approximation was selected for its higher probability of giving the accurate output result than the truncation. In which does not variably outputs 0 irrespective of the input.

Fig.2 1-bit DMFA

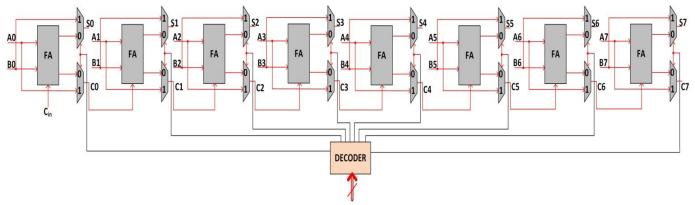

In figure 2 shows the logic block diagram of the dual mode full adder cell (DMFA), when replace the constituent full adder cells of an 32-bit Ripple Carry Adder as shown in the figure of 3.

In addition, it is also consists of the approximation controller for generating the appropriate select signals for the multiplexers. From the point of controlling the approximation magnitude

TABLE 1

POWER CONSUMPTION OF DIFFERENT DMFA MODES

| Original | DMFA accurate | DMFA approximate |

|----------|---------------|------------------|

| FA(μw)   | mode(μw)      | mode(μw)         |

| 1.53     | 1.74          | 0.01             |

by using a Multimode full adder cell. Because multimode full adder cell would provide even a better alternative to the dual-mode full adder. It also improve the complexity in the decoder block, it is used for select the right signals to the multiplexers as well as logic overhead for the multiplexers themselves.

#### DMFA overhead

Dual-mode full adder is consists the power gating transistor and the multiplexers are design to incur the possible over head. Dual-Mode full adder experiments show that the switching power of the CMOS transistors contributes toward the most of the total power consumption of the full adder and dual-mode full adder blocks.

Table 1 shows Difference between the power consumption of the full adder and dual-mode full adder for different modes obtained by Xilinx 13.2 version. It shows that the power improved by  $0.21\mu w$  when we operate Dual-mode full adder in accurate mode as compared to the original mode.

It shows the power consumed during the dual-mode full adder approximate mode is almost removed when compared with the accurate mode. In Which is due to power gating of the full adder block by the Pmos transistor. To reduce the input switching activity of the multiplexers is also a secondary cause for this low amount of power.

The additional overhead is used to switching of the power gating transistor can be rejected, hence it is switching algorithms. This is mainly due to the spatial and temporal locality of the pixel values across the consecutive frames.

The concept of the adder/subtractor blocks is extend to other adder architectures as well. Adder architecture is consists CBA and CSA, which also contain full adder as the fundamental building blocks, can be made accuracy configurable by direct substitution of the full adders with DMFAs.

Fig.3. 8-bit reconfigurable RCA blocks

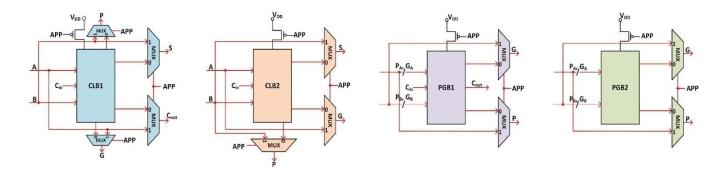

Fig. 4 1-bit dual-mode carry propagate generate blocks.

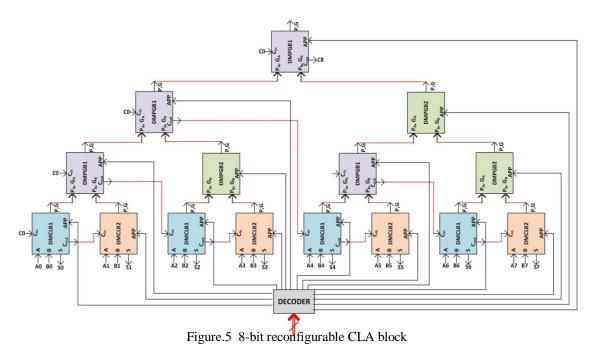

As an example, I implemented a 32-bit carry lookahead adder consisting four different types of basic blocks figure 5 depending upon the presence of sum (s), Cout, carry propagation (P), and carry generation (G) at different levels. To address this blocks present at the first level or the lowest level of a carry lookahead adder (CLA), which have inputs is coming directly, as carry lookahead adder blocks, such CLB1 and CLB2.

The difference among the CLB1 produces an additional Cout signal compared with CLB2. Their corresponding to the dual-mode versions, DMCLB1 and DMCLB2, have both sum S and propagate P approximated by input operand B and both Cout and generate G approximated by input operand A, as shown in figure 4. The basic blocks present in the higher levels of carry look ahead adder CLA hierarchy are represented as the configurable as propagate P and generate G blocks, PGB1 and PGB2.

In this case PGB1 generate an extra Cout output as compared with PGB2. As shown in figure 4, the configurable dual-mode versions, DMPGB 1 and DMPGB 2, use inputs Pa and Pb as approximations for outputs propagate and generate. These approximations ensuring that the ratio of the probability of match output to the additional circuit overhead for each of the blocks is large. Table 2 shows and realize the additional circuit overhead for each of the Dual-mode full adder blocks. When operating in either accurate or else approximate mode. Reconfigurable of Carry lookahead adder (CLA), Dual-mode carry lookahead blocks such as DMCLB1 and DMCLB2 blocks are approximated in according with the Dual-mode (DA).

However the Dual-mode propagate generator blocks such as DMPGB1 and DMPGB2 blocks approximated when each and every Dual-mode carry propagate generator blocks such as DMCLB1, DMCLB2, DMPGB1 and DMPGB2 block, which belongs to the transitive fan-in cones of the concerned block is approximated.

Otherwise, the block is performed in the accurate mode. For example, any Dual-mode propagate generator blocks (DMPGB) block at the second level of the carry lookahead adder (CLA) can be performed in approximate mode, and both of its constituent DMCLB1 and DMCLB2 blocks are performed in the approximate mode. In each DMPGB block can be approximated only when both of its constituent DMPGB1 and DMPGB2 blocks are approximated. This architecture can be realize extrapolated to other similar type Carry lookahead adders (CLAs), and so on.

TABLE 2

#### DUAL-MODE BLOCK OUTPUTS FOR ACCURATE AND APPROXIMATE MODES

| Basic block   | Output for APP=0 | Output for APP=1   |

|---------------|------------------|--------------------|

| (adder type)  | (accurate mode)  | (approximate mode) |

| DMFA          | S=A±B±Cin        | S=B                |

| (RCA,CBA,CSA) |                  | Cout=A             |

| DMCLB1        | $P=A\pm B$       | P=B                |

| (CLA)         | G=AB             | G=A                |

|               | S=P±Cin          | S=B                |

|               | Cout=G+PCin      |                    |

| DMCLB2        | P=A±B            | P=B                |

| (CLA)         | G=AB             | G=A                |

|               | S=P±Cin          | S=B                |

| DMPGB1        | P=PA PB          | P=PA               |

| (CLA)         | G=GB+GAPB        | G=GB               |

|               | Cout=G+PCIN      | Cout=G+PCin        |

| DMPGB2        | P=PA             |                    |

| (CLA)         | G=GB             |                    |

Figure 6 and 7 represent a comparative study of the power consumption of the different types of adders, when the Degree of approximation DA is differed. In particular, the figure denote the normalized power consumption of the different types of RABs when the number of bits approximated is differed. An observation for Carry select adder CSA is that approximating its MSBs produce largest power savings than the LSB approximation per bit.

To the architecture of the carry save adders, where approximating each bit in the MSB results in power gating of two full adders compared with one full adder when the LSBs are approximated.

This is the point, where the savings due to the addition al multiplexers, power gating transistors, and controller. The inherent error resilience represented by the motion estimation ME and the small inputs to the DCT block gives sufficient opportunities for achieving a high degree of approximation (much greater than 5) and thereby high power savings.

Fig.6 output quality for different error bounds on PSNR

In figure 6 shows the snapshots of the output for Garden when evaluated using proposed approximate architecture. We observe higher distortion of video quality for more relaxed PSNR degradation bounds.

### V. CONCLUSION

This paper proposed a reconfigurable approximate architecture for the MPEG encoders that optimize power consumption while maintain a output quality across different input videos. The proposed architecture is based on the input characteristics. It requires the user to specify only the overall minimum quality for videos instead of having to decide the level of hardware approximation. Our experimental results show that the proposed architecture results in power savings equivalent to a baseline approach that uses fixed approximate hardware while respecting quality constraints across different videos. Future work includes the incorporation of other approximation techniques and extending the approximations to other arithmetic and functional blocks.

#### **REFERENCES**

- [1] M. Elgamel, A. M. Shams, and M. A. Bayoumi, "A comparative analysis for low power motion estimation VLSI architectures," in *Proc. IEEE Workshop Signal Process. Syst. (SiPS)*, Oct. 2000, pp. 149–158.

- [2] F. Dufaux and F. Moscheni, "Motion estimation techniques for digital TV: A review and a new contribution," *Proc. IEEE*, vol. 83, no. 6, pp. 858–876, Jun. 1995.

- [3] I. S. Chong and A. Ortega, "Dynamic voltage scaling algorithms for power constrained motion estimation," in *Proc. IEEE Int. Conf. Acoust., Speech, Signal Process. (ICASSP)*, vol. 2. Apr. 2007.

- [4] I. S. Chong and A. Ortega, "Power efficient motion estimation using multiple imprecise metric computations," in *Proc. IEEE Int. Conf. Multimedia Expo*, Jul. 2007.

- [5] D. Mohapatra, G. Karakonstantis, and K. Roy, "Significance driven computation: A voltage-scalable, variation-aware, quality-tuning motion estimator," in *Proc. 14th ACM/IEEE Int. Symp. Low Power Electron. Design (ISLPED)*, 2009.

- [6] J. George, B. Marr, B. E. S. Akgul, and K. V. Palem, "Probabilistic arithmetic and energy efficient embedded signal processing," in *Proc. Int. Conf. Compil.*, *Archit.*, *Synth. Embedded Syst. (CASES)*, 2006.

- [7] D. Shin and S. K. Gupta, "A re-design technique for datapath modules in error tolerant applications," in *Proc.* 17th Asian Test Symp. (ATS), 2008.

- [8] S. Venkataramani, A. Sabne, V. Kozhikkottu, K. Roy, and A. Raghunathan, "SALSA: Systematic logic synthesis of approximate circuits," in *Proc. 49th Annu. Design Autom. Conf. (DAC)*, Jun. 2012.

- [9]V. Gupta, D. Mohapatra, S. P. Park, A. Raghunathan, and K. Roy, "IMPACT: IMPrecise adders for low-power approximate computing," in *Proc. 17th IEEE/ACM Int. Symp. Low-Power Electron. Design (ISLPED)*, Aug. 2011.

- [10] V. Gupta, D. Mohapatra, A. Raghunathan, and K. Roy, "Lowpower digital signal processing using approximate adders," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 32, no. 1, Jan. 2013.

- [11] V. G. Moshnyaga, K. Inoue, and M. Fukagawa, "Reducing energy consumption of video memory by bit-width compression," in *Proc. Int. Symp. Low Power Electron. Design (ISLPED)*, 2002.

- [12] Z. He and M. L. Liou, "Reducing hardware complexity of motion estimation algorithms using truncated pixels," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, vol. 4. Jun. 1997.

- [13] Z.-L. He, C.-Y. Tsui, K.-K. Chan, and M. L. Liou, "Low-power VLSI design for motion estimation using adaptive pixel truncation," *IEEE Trans. Circuits Syst. Video Technol.*, vol. 10, no. 5, Aug. 2000.

- [14] A. Raha, H. Jayakumar, and V. Raghunathan, "A power efficient video encoder using reconfigurable approximate arithmetic units," in *Proc. 27th Int. Conf. VLSI Design, 13th Int. Conf. Embedded Syst.*, Jan. 2014.

- [15] P. M. Kuhn, *Algorithms, Complexity Analysis and VLSI Architectures for MPEG-4 Motion Estimation*, 1st ed. Norwell, MA, USA: Kluwer, 1999.